本文最后更新于 209 天前,其中的信息可能已经有所发展或是发生改变。

写在前面,这些知识点基本都是非计算题,主要是为了方便自己的复习,同时放在自己博客上或许可以帮助到其他同学。下面的内容是结合课程PPT和往年题目总结的,有检查过,应该没有错误,如有错误,还烦请各位指出。

一、往年已考知识点

1. 集成电路发展的特点

- 特征尺寸越来越小

- 晶圆尺寸越来越大

- 芯片集成度越来越高

- 时钟速度越来越高

- 电源电压越来越低

- 布线层数越来越多

2. 集成电路材料

- 导体

- 半导体

- 绝缘体(例如,陶瓷等)

3.集成电路制造的主要工艺及作用

- 主要有氧化、掺杂和光刻工艺

- 作用:氧化工艺用于制备

薄膜;参杂工艺是在半导体基片的一定区域掺入一定浓度的杂质元素形成不同类型的半导体层来制作各种器件;光刻工艺是实现掩膜版图形到硅片表面各种薄膜上图形的转移。

4.

- 作为对杂质选择扩散区域的掩膜

- 作为 MOS 器件绝缘层的绝缘栅材料(栅氧)

- 作为器件之间、层间的隔离材料(场氧)

- 作为器件表面的保护(钝化)膜

- 作为制作集成电路介质

5. 掺杂工艺主要有扩散工艺和离子注入工艺

6. CMOS工艺中的阱的类型有

- P阱

- N阱

- 双阱

7. 版图设计规则相关问题

内容:设计规则规定了几何图形的最小宽度、最小间隔、最小延伸、最小交叠以及层间的最小距离。

设计规则的作用:是设计和生产之间的一个桥梁是一定的工艺水平下电路的性能和成品率的最好的折中。

设计规则描述:

- 微米设计规则:以微米为单位直接描述版图的最小允许尺寸。

设计规则:以 为基准的,最小允许尺寸均表示为 的整数倍。 近似等于将图形移到硅表面上可能出现的最大偏差;如限制最小线宽为 ,窄了线条就可能断开 可以随着工艺的改进线性缩小,这就使设计变得更加灵活。

8. 常用的可测性设计方法主要有

- 特设法

- 扫描路径法,常考:扫描路径法的基本原理

- 内设自测试法(BIST)

- 边界扫描法

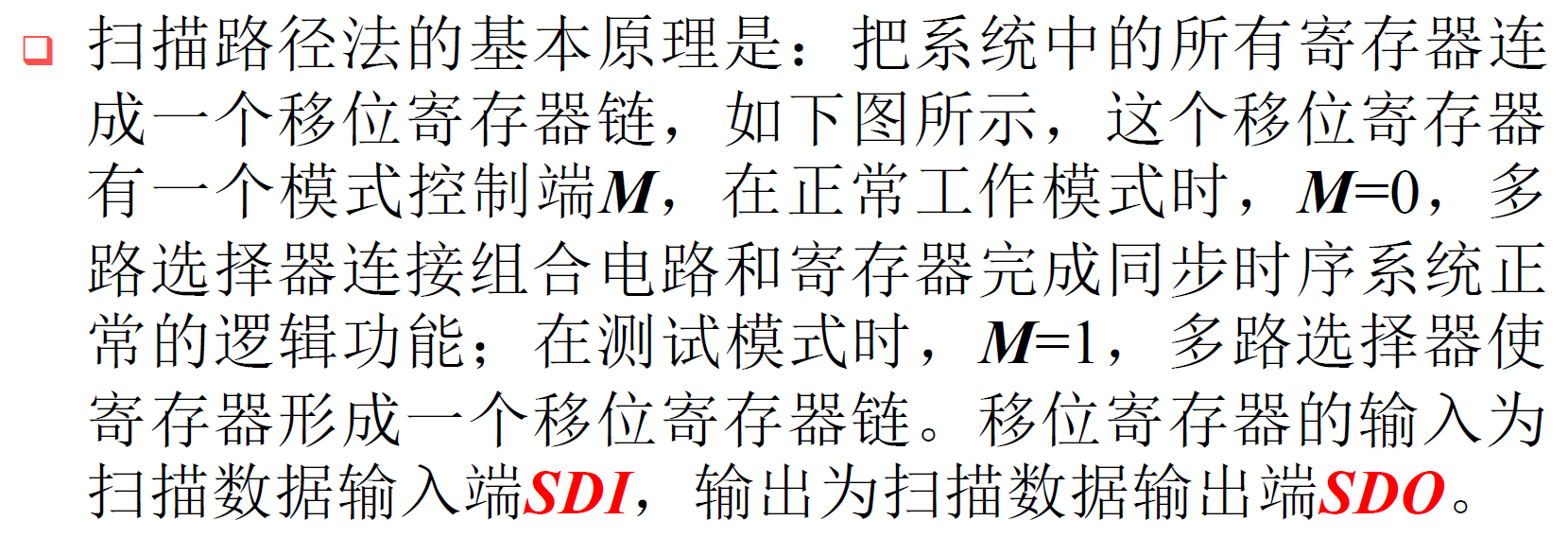

9. 扫描路径法的基本思想和基本原理

- 基本思想:一个同步时序系统一般可看成由组合电路(下一个状态电路和输出电路 )和时序电路两部分组成,如果能把这两部分分开测试将大大降低测试的复杂度。扫描路径法就是这样一种测试同步时序系统的方法 。

- 基本原理:

10. 有限状态机通常分为哪两类?二者有什么区别?

通常分为米利(Mealy)型和摩尔(Moore)型,Mealy型的输出不仅取决于当前状态,还和输入有关;Moore型的输出仅取决于当前状态。

二、往年未考知识点

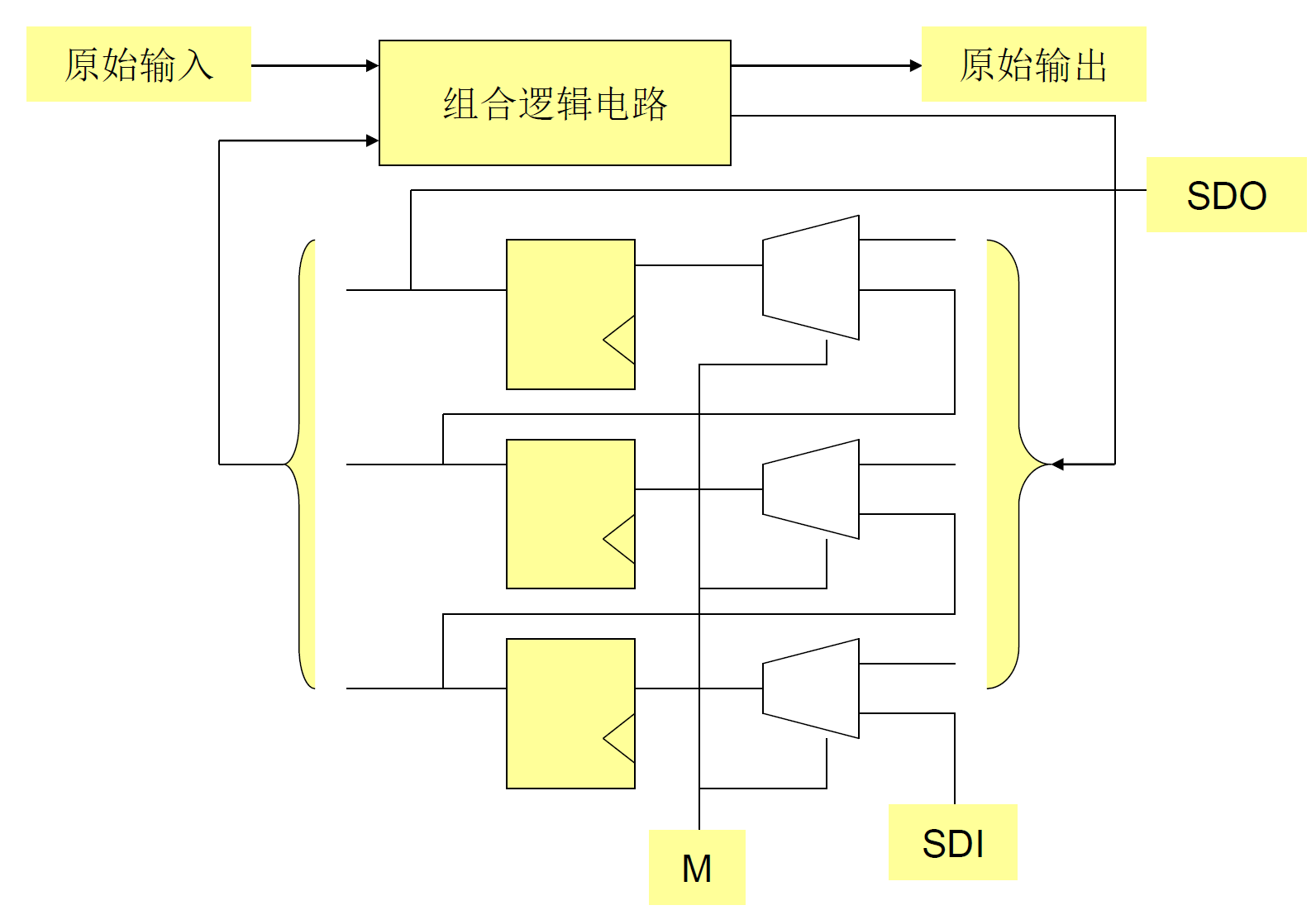

1. 集成电路的分类

2. 导体、半导体和绝缘体在集成电路制造工艺中的功能

3. 多晶硅的用途

- 电阻

- 互连线

- MOS器件的栅极

4. 集成电路制造的关键问题就是根据设计要求在半导体的不同区域形成所需要的PN结这在生产上主要是通过氧化 、掺杂 、光刻等多种工艺的多次反复而形成 。

5. 集成电路元器件

- MOS管

- 电容

- 电阻

- 电感

- 连线

6. 可测性设计应考虑的问题:

- 变不可测故障为可测故障

- 测试数据生成的时间应尽量少

- 测试数据应尽量少

7. 扫描路径法的优缺点及改进

8. Verilog中阻塞赋值和非阻塞赋值有什么区别

阻塞赋值操作符用等号("=")表示,非阻塞赋值操作符用小于等于号 ("<=")表示。

- 在时序逻辑电路中一般使用非阻塞赋值。非阻塞赋值在块结束后才完成赋值操作,此赋值方式可以避免在仿真出现冒险和竞争现象;

- 在组合逻辑电路中一般使用阻塞赋值。使用阻塞方式对一个变量进行赋值时,此变量的值在在赋值语句执行完后就立即改变;

- 在

assign语句中必须使用阻塞赋值语句。

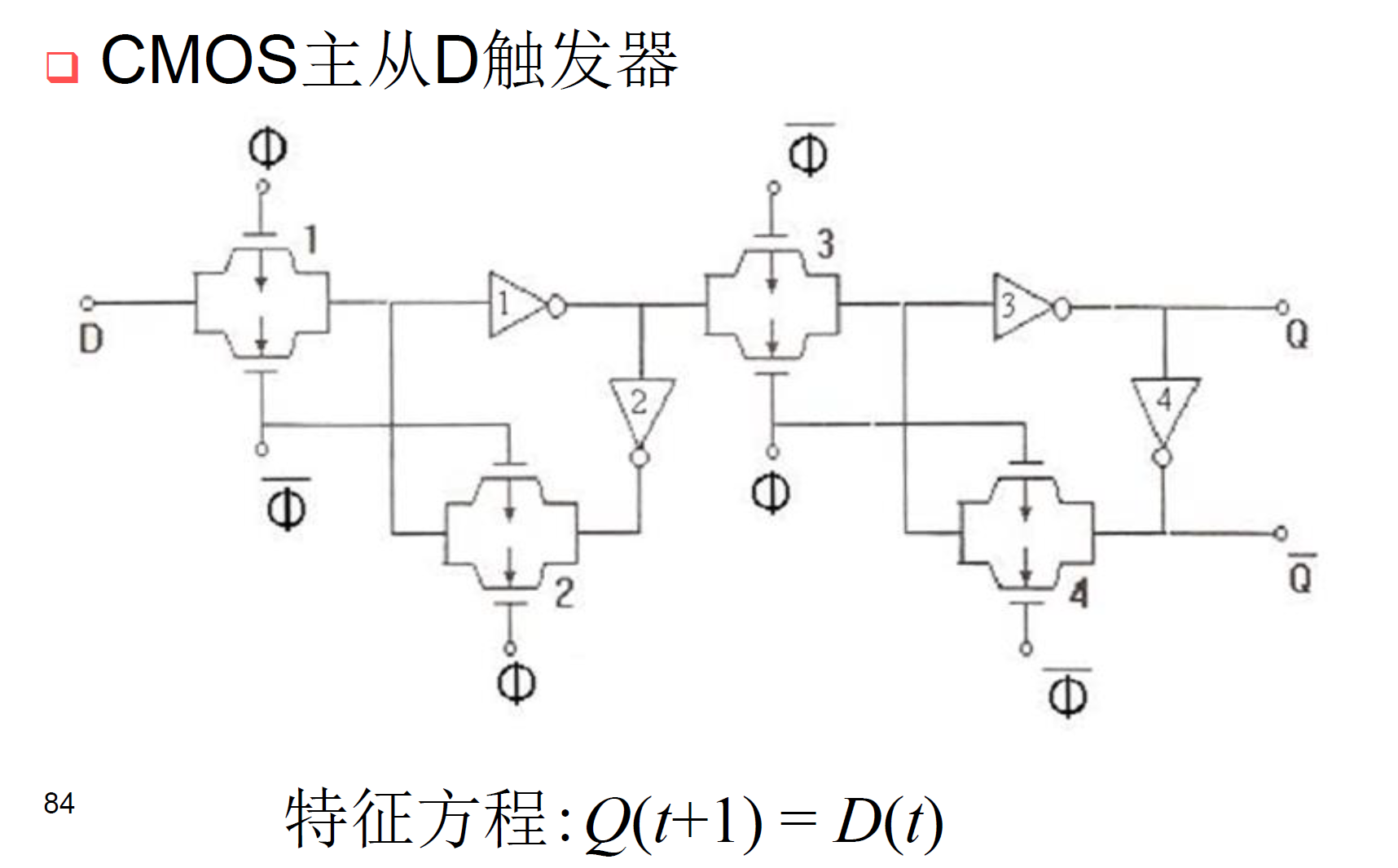

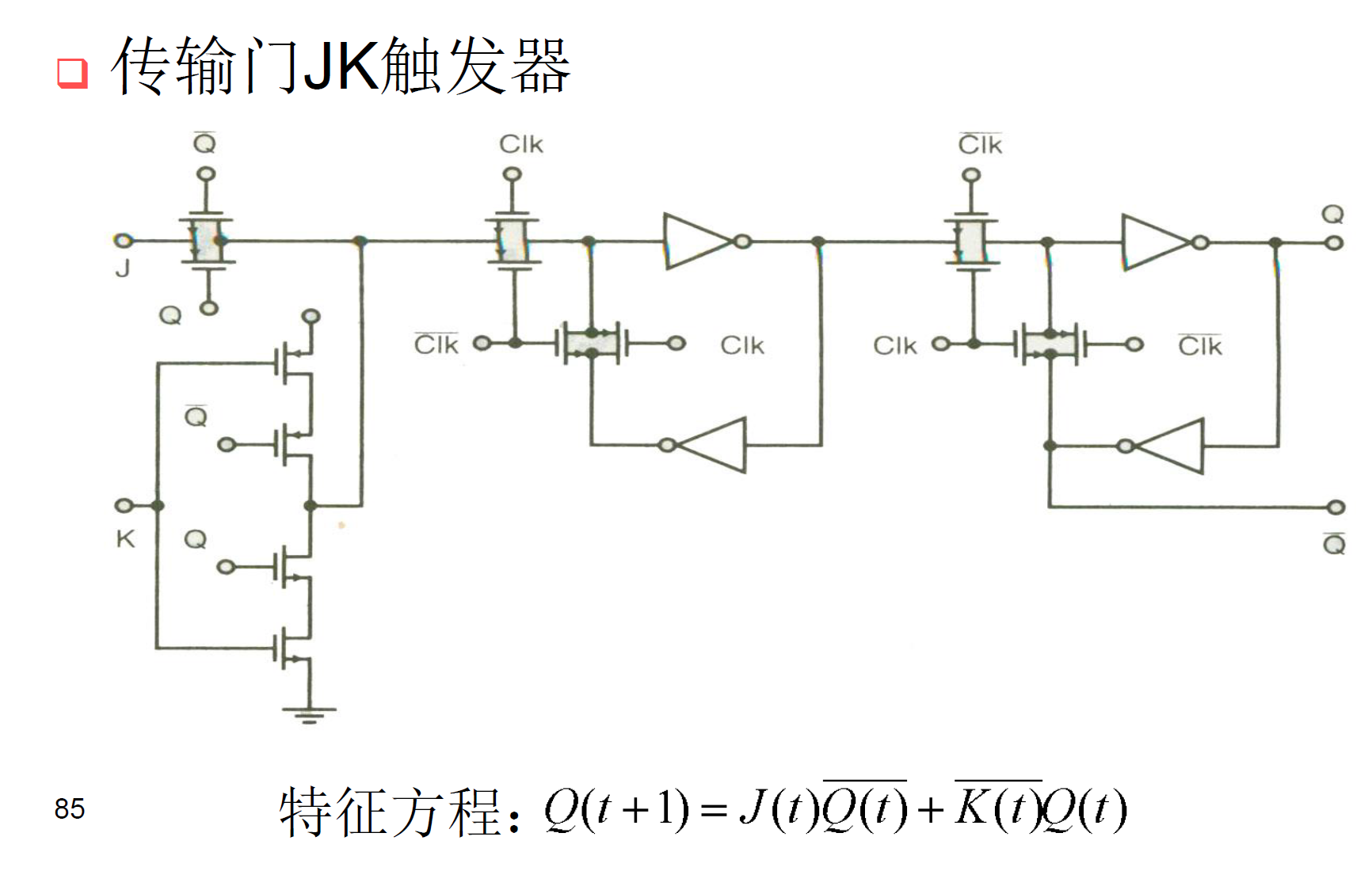

9. 触发器

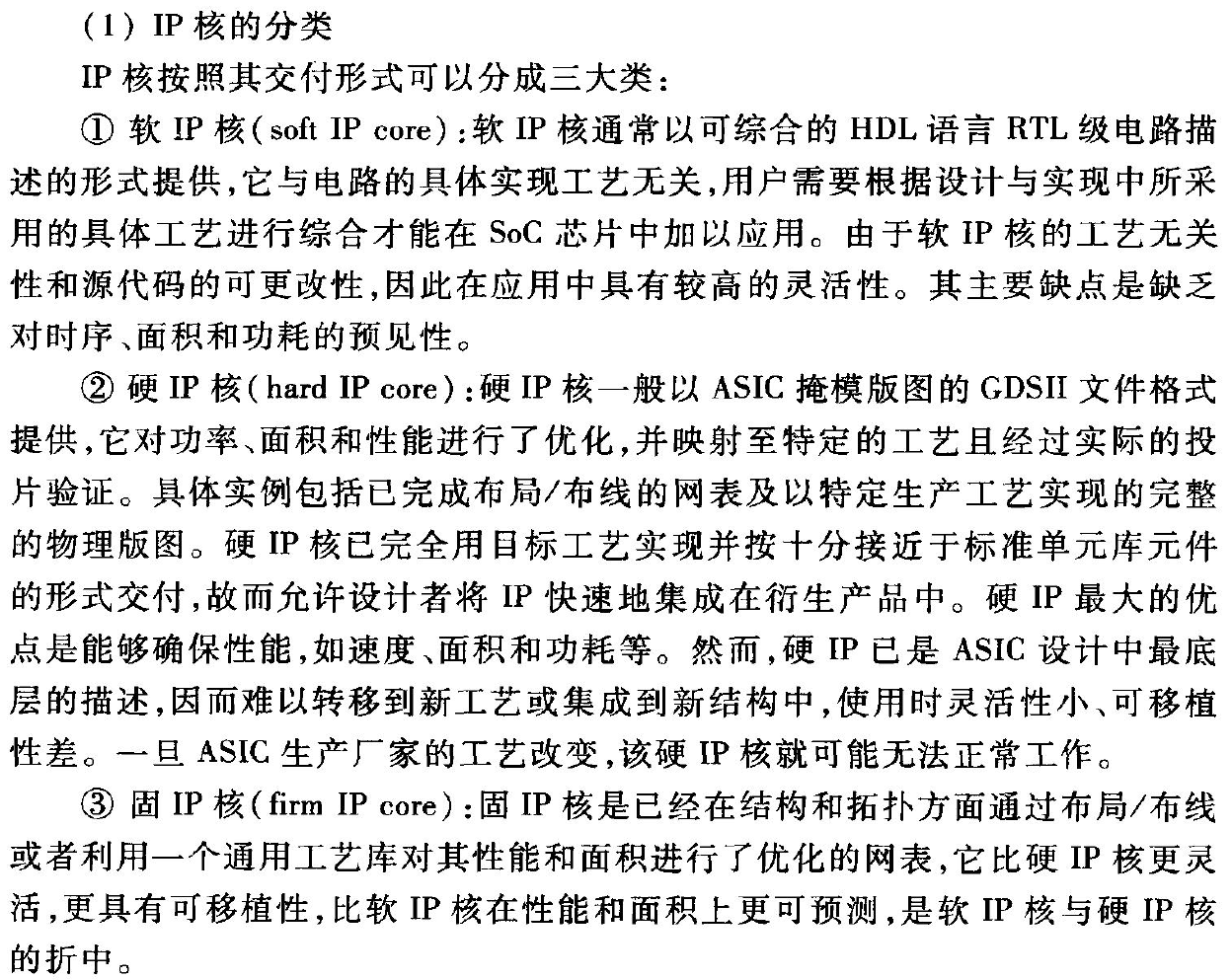

10. IP核的分类及区别

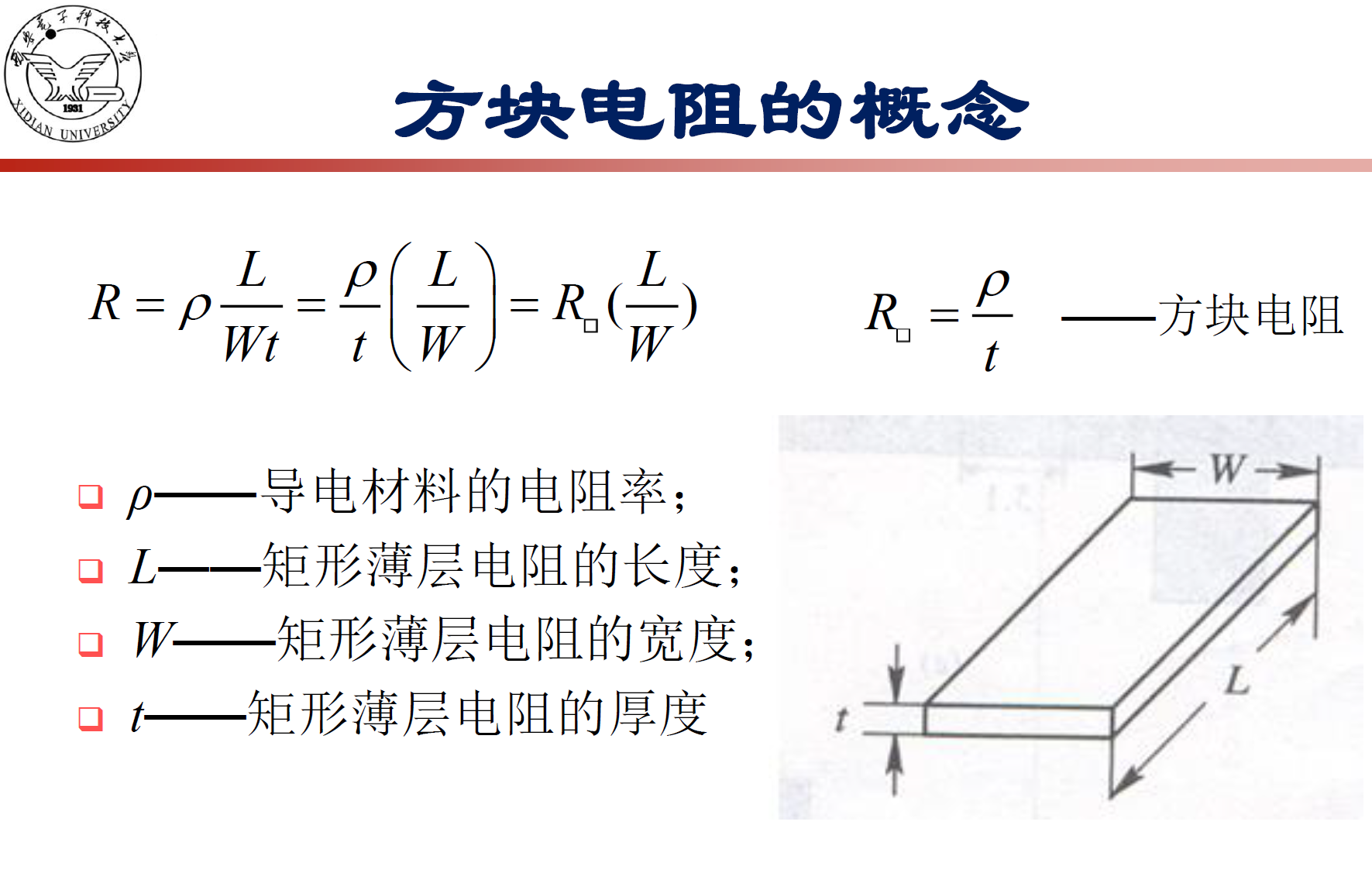

11. 方块电阻

三、常见Verilog代码

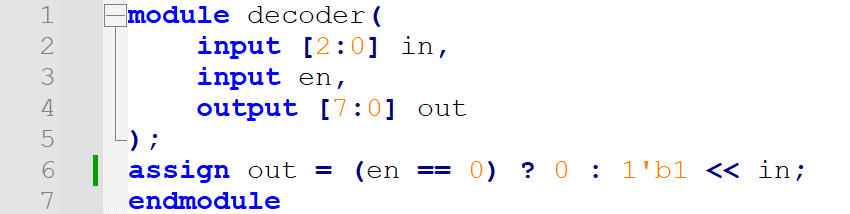

1. 3/8译码器

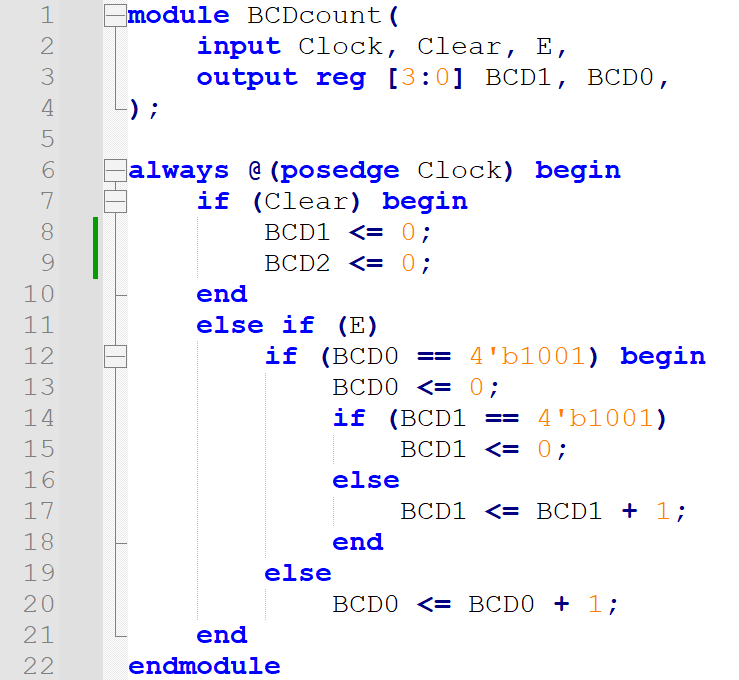

2. 2位BCD码

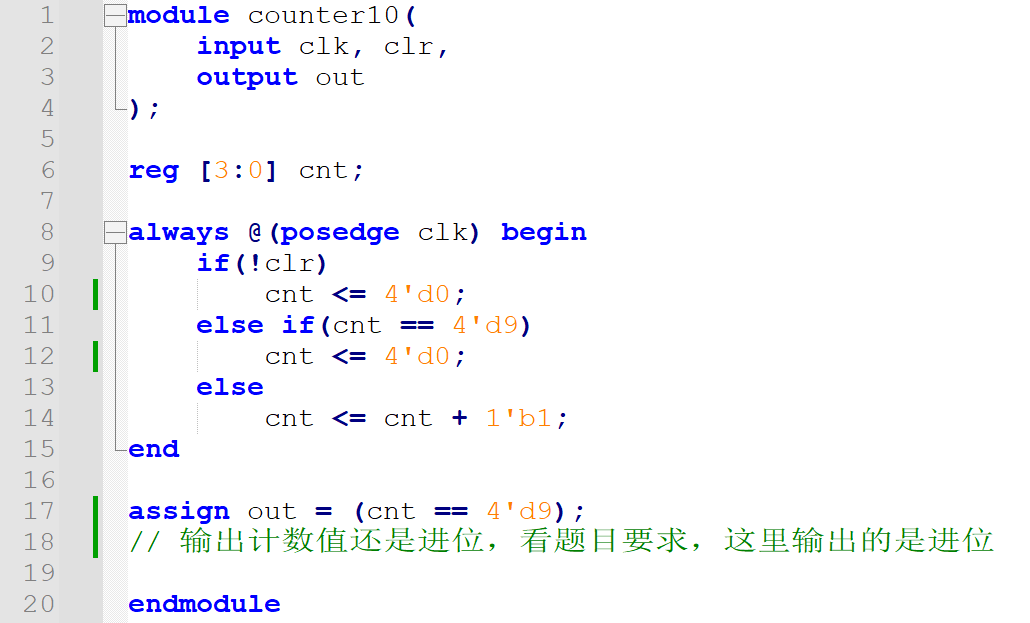

3. 十进制计数器

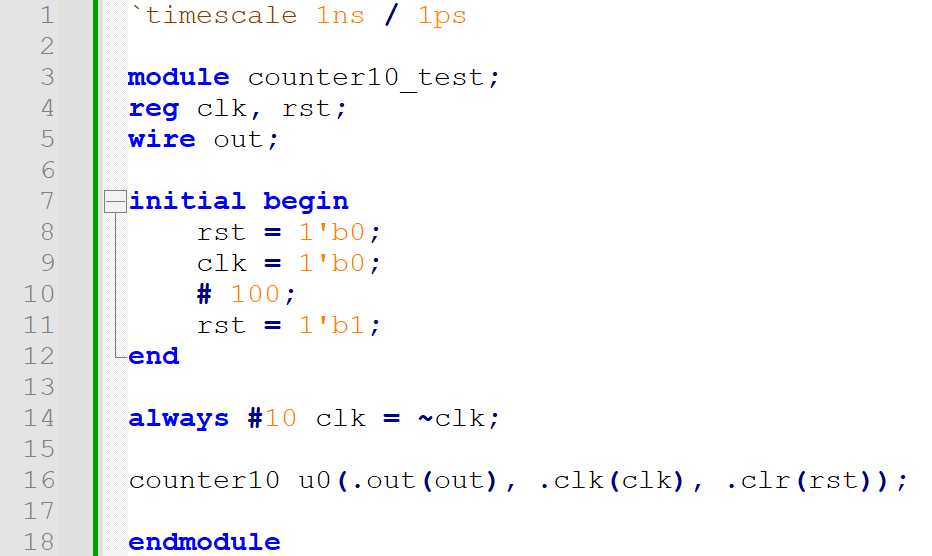

4. 十进制计数器的测试文件(testbench)

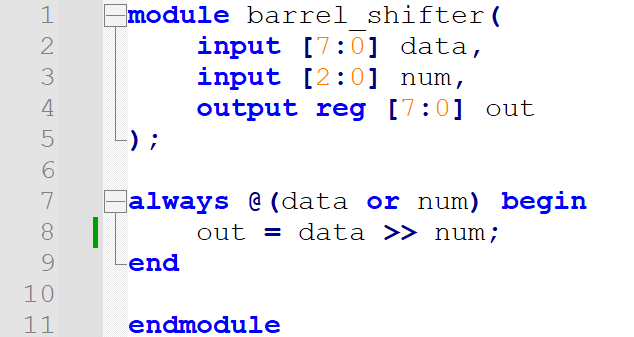

5. 8位逻辑右移移位器